C++_makefile基础

好处:一次编写,终身受益

命名规则:

makefile、Makefile三要素:目标、依赖、规则命令

1. makefile编写

写法:

目标(target): 依赖(prerequiries)...

tap键 规则命令(command)- 目标(target)通常是要产生的文件的名称,目标的例子是可执行文件或OBJ文件。目标也可是一个执行的动作名称,诸如‘clean’(仅仅表达动作的目标称为假想目标)。

- 依赖是用来输入从而产生目标的文件,一个目标经常有几个依赖。

- 命令是

make执行的动作,一个规则可以含有几个命令,每个命令占一行。

注意:每个命令行前面必须是一个Tab字符,即命令行第一个字符是Tab。这是不小心容易出错的地方。

makefile举例:

编写add.c、sub.c、test.h文件:

add.c:

#include"test.h"#include<stdio.h>intadd(int a,int b){return a+ b;}intmain(){printf(" 2 + 3 = %d\n",add(2,3));printf(" 2 - 3 = %d\n",sub(2,3));return1;}sub.c:

#include"test.h"intsub(int a,int b){return a- b;}test.h:

#ifndef _TEST_H#define _TEST_Hintadd(int a,int b);intsub(int a,int b);#endifmakefile:

test: add.o sub.o

gcc -otest add.o sub.o

add.o: add.c test.h

gcc -c add.c

sub.o: sub.c test.h

gcc -c sub.c

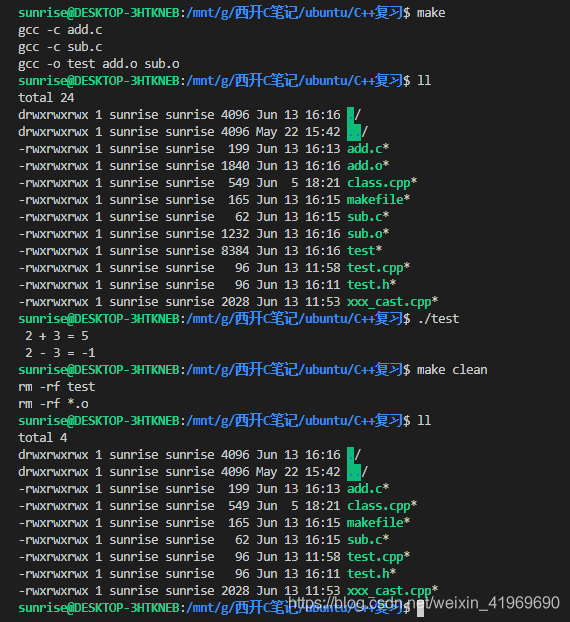

clean:rm -rftestrm -rf *.o2. 执行makefile文件

在命令行输入:

make如果有多个makefile文件,需要指定makefile文件进行make,需要加参数-f:

make -f Make_test

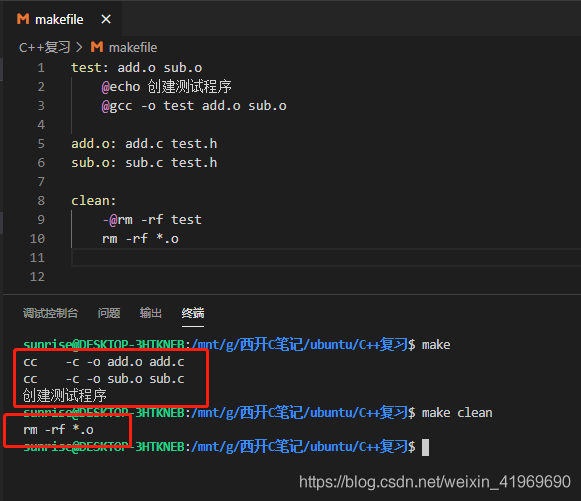

3. 高级makefile写法(重要)

目标:依赖

规则命令这里的规则命令有时可以省去不写,编译器自动推导。

规则这里可以添加@echo+语句命令,用来打印当前语句

规则前也可添加@符号,表示不打印此行规则。

规则添加-@符号,表示如果该命令报错,也要继续运行。

示例:

test: add.o sub.o

@echo 创建测试程序

@gcc -otest add.o sub.o

add.o: add.c test.h

sub.o: sub.c test.h

clean:

-@rm -rftestrm -rf *.o

(1)两个重要的函数:

wildcard:可以进行文件匹配patsubst:内容的替换(2)使用变量的方法:

$(变量)(3)使用通配符:

%作为通配符

从匹配目标格式的目标名中依据通配符抽取部分字符串,再按照抽取字符串分配到每一个依赖格式中产生依赖名。例如,使用%.o:%.c(4)$的搭配用法:

$@:目标$^:全部依赖$<:第一个依赖$?:第一个变化的依赖

SrcFiles=$(wildcard *.c)#注释:可以得到所有的.c文件

ObjFiles=$(patsubst %.c,%.o,$(SrcFiles))#把所有的.c文件替换成.o文件

.RHONY:clean#防止有歧义

all:app#伪目标

app:$(ObjFiles)

gcc -o app $^

%.o:%.c#把每一个.c生成.o

gcc -o$@ -c $^#此处$^可以更换为$<

clean:rm -rf$(ObjFiles) appgcc可以更换为$(CC)变量

一些参数(比如-fPIC)可以定义到$(CFLAGS)变量里

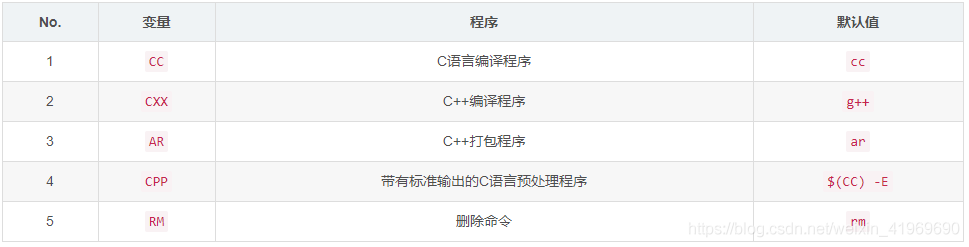

预定义变量

预定义变量是makefile已经定义好的变量,用户可以在makefile文件中改变变量的值。

程序名变量

程序运行参数的变量

其他注释

#换行

\回显命令

@echo